| RESEARCH GROUP                    |             |               | olar Decoding                                          |

|-----------------------------------|-------------|---------------|--------------------------------------------------------|

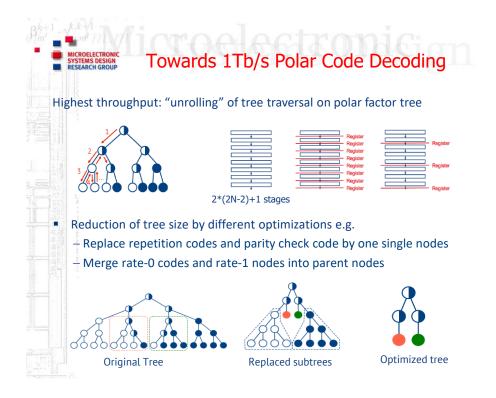

| 024/512 Code, fast SC d           | ecoding alg | gorithms      |                                                        |

| Worst case PVT timing             | g 28nm tec  | hnology, opti | mized factor tree                                      |

| Logic stages 385, retin           | ned pipelin | e stages 105  | (f ~ 600MHz)                                           |

| 0 0 ,                             |             | U             | ,                                                      |

| Place&Route                       | Dogistor    | Latches       |                                                        |

|                                   | Register    |               |                                                        |

| Area [mm <sup>2</sup> ]           | 3.14        | 2.79          |                                                        |

| - Combinat.                       | 0.96        | 0.91          |                                                        |

| - Buf/Inv                         | 0.65        | 0.27          |                                                        |

| - Noncomb                         | 1.55        | 1.12          |                                                        |

| Area Eff. [Gbps/mm <sup>2</sup> ] | 205         | 231           | 一名: "我们就帮你帮助                                           |

| Utilization                       | 78%         | 72%           |                                                        |

| Frequency [MHz]                   | 621         | 629           | Contract of the state of the                           |

| Throughput [Gbps]                 | 636         | 644           |                                                        |

| Power [W]                         | 5.7         | 2.7           | - States - Andrew                                      |

| - Clock                           | 47%         | 19%           | and the second second                                  |

| - Registers                       | 24%         | 13%           |                                                        |

| - Combinat.                       | 29%         | 68%           |                                                        |

| Energy Eff. [pJ/bit]              | 8.8         | 4.2           | Each colour represents a stag<br>black color is memory |

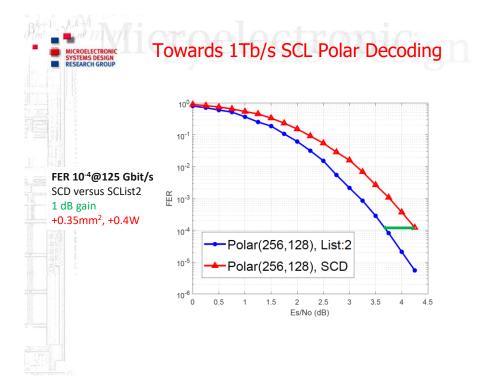

## Towards 1Tb/s SCL Polar Decoding

256/128 Polar Code

Worst case PVT timing 28nm, optimized tree, retiming, latch based design

SC vs SCL2, SCL4 @ 125Gbit/s

| Place & Route              | SC     | SCL L2 | SCL L4 |

|----------------------------|--------|--------|--------|

| Frequency (MHz)            | 493    | 485    | 481    |

| Throughput (Gbps)          | 126.1  | 124.3  | 123.1  |

| Core Area (mm2)            | 0.2270 | 0.5899 | 1.3754 |

| Area Efficiency (Gbps/mm2) | 556    | 211    | 89     |

| Utilization %              | 69     | 71     | 74     |

| Power Total (W)            | 0.200  | 0.634  | 1.587  |

| Energy Efficiency (pJ/bit) | 1.59   | 5.11   | 12.89  |

| Power Density (W/mm2)      | 0.88   | 1.08   | 1.15   |

SCL4, each colour represents a logic stage, black color is memory

|                                                                           | ards 1 <sup>-</sup> | Tb/s S | CL Po  | olar D | Decoding                                                             |

|---------------------------------------------------------------------------|---------------------|--------|--------|--------|----------------------------------------------------------------------|

| 512/427 Polar Code SCL [<br>Worst case PVT timing<br>Normalized to same f | g 28nm teo          | 0,     |        |        |                                                                      |

| [1] 28nm technology (WC<br>Better energy than [1                          |                     |        | ghput  |        | 1 page                                                               |

| Place & Route                                                             | SC                  | SCL L2 | SCL L4 | [1]    |                                                                      |

| Frequency (MHz)                                                           | 493                 | 397    | 400    | 468    | SCL4, each colour represents a logic stage,<br>black color is memory |

| Throughput (Gbps)                                                         | 252.2               | 203.2  | 204.8  | (12.0  | >                                                                    |

| Core Area (mm2)                                                           | 0.4235              | 1.4872 | 3.2581 | 0.8700 |                                                                      |

(137

1.266

6.23 12.77

14

0.087

7.25

63

2.615

| Power Density (W/mm2)                                                                | 1.26     | 0.85        | 0.80       | 0.10          |

|--------------------------------------------------------------------------------------|----------|-------------|------------|---------------|

| [1] P. Giard, A. Balatsoukas-Stimming, T.<br>multi-Gbps unrolled hardware list decod |          | , 0,        |            | , ,           |

| Asilomar Conference on Signals, System                                               | s and Co | mputers, Pa | cific Grov | ve, CA, 2016. |

596

0.535

2.12

Area Efficiency (Gbps/mm2)

Energy Efficiency (pJ/bit)

Power Total (W)

Thank you for attention! For more information please visit http://ems.eit.uni-kl.de